Energy-Aware Interconnect Resource Reduction Through Buffer Access Manipulation for Data-Centric Applications

Product Description

Energy-Aware Interconnect Resource Reduction Through Buffer Access Manipulation for Data-Centric Applications

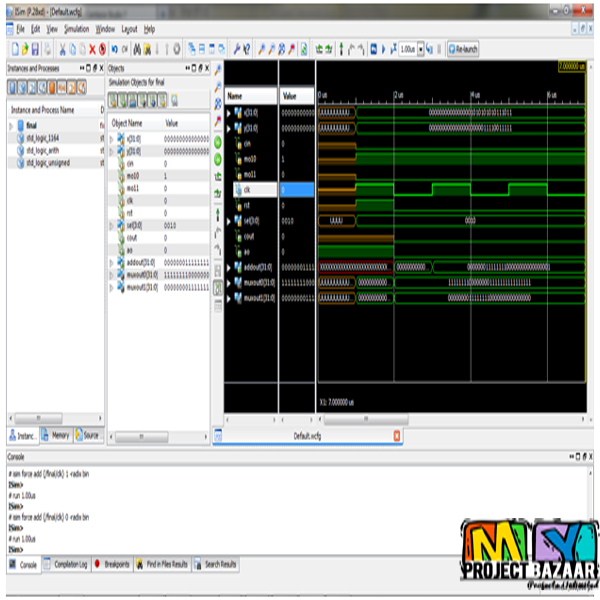

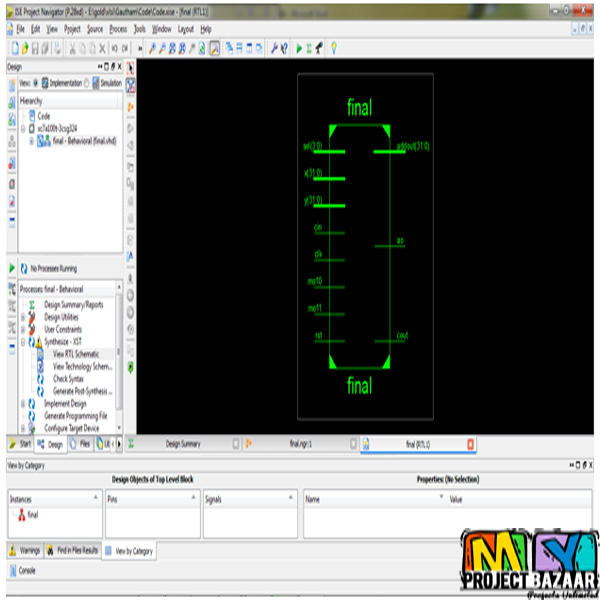

Abstract— Energy-Aware Interconnect Resource Reduction Through Buffer Access Manipulation for Data-Centric Applications.This paper presents a methodology for reducing interconnect resources in reconfigurable platforms such as field-programmable gate arrays (FPGAs). This methodology utilizes the techniques developed for the buffer-based dataflow, a new design representation suitable for implementing data-centric applications in a reconfigurable platform. In a buffer-based dataflow, nodes correspond to processing blocks and buffer controllers represent the interconnects between the processing blocks. Since we can isolate the functional execution and data transfer of each node by using buffer controllers, < Final Year Projects > a buffer-based dataflow is helpful for reducing overall design time and for increasing reconfigurability. In this paper, we propose a sharing methodology that can reduce the buffer memory and the number of buses used in the realization of a buffer-based dataflow. By reducing the resources allocated to buffer controllers, we can achieve interconnect resource reduction. The proposed sharing methodology can increase the dynamic energy consumption due to the increased port-loading capacitance. By using the energy consumption model determined by the costs of buffers and buses, we investigate whether the sharing case with the minimum resources corresponds to the sharing case consuming the minimum energy or not. We evaluate the proposed sharing methodology with the dataflow graphs representing data-centric applications such as SIRF, IPv4, MC-CDMA transmitter and receiver.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet