A Normal I/O Order Radix-2 FFT Architecture to Process Twin Data Streams for MIMO

Product Description

A Normal I/O Order Radix-2 FFT Architecture to Process Twin Data Streams for MIMO

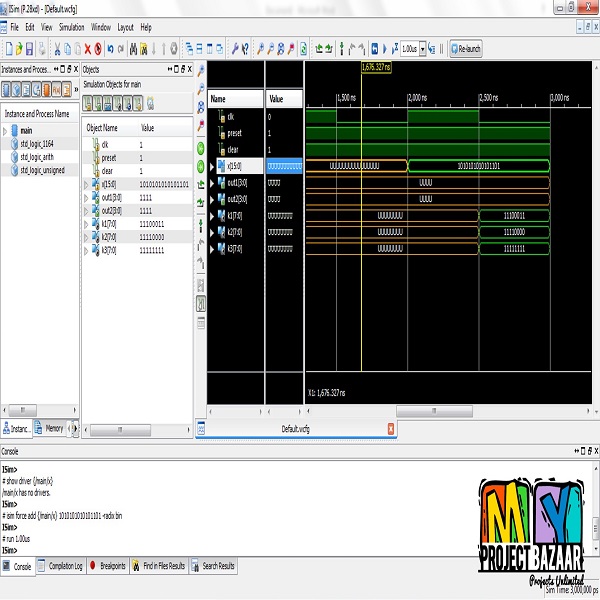

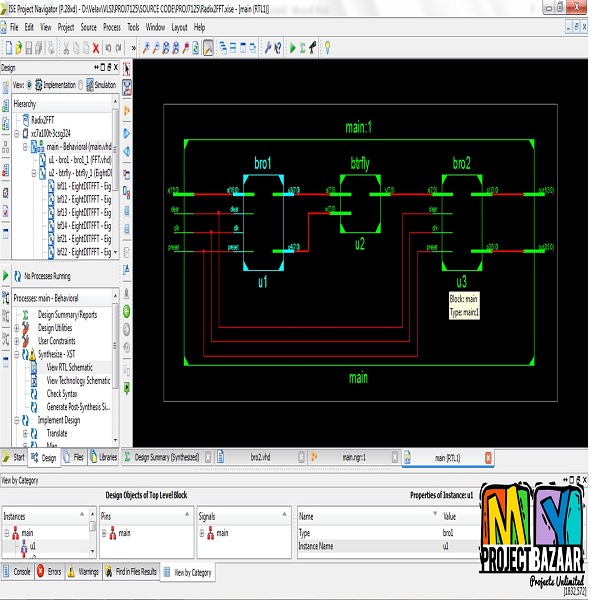

Abstract— Many applications require simultaneous computation of multiple independent fast Fourier transform (FFT) operations with their outputs in natural order. Therefore, this brief presents a novel pipelined FFT processor for the FFT computation of two independent data streams. The proposed architecture is based on the multipath delay commutator FFT architecture. It has an N /2-point decimation in time FFT and an N /2-point decimation in frequency FFT to process the odd and even samples of two data streams separately. The main feature of the architecture is that the bit reversal operation is performed by the architecture itself, so the outputs are generated in normal order without any dedicated bit reversal circuit. The bit reversal operation is performed by the shift registers in the FFT architecture by interleaving the data. Therefore, the proposed architecture requires a lower number of registers and has high throughput. The proposed architecture is designed to process two independent data streams simultaneously with less amount of hardware. The odd inputs, which are in natural order, are first bit reversed and then they are processed by N /2-point decimation in time (DIT) FFT. The even samples are directly processed by N /2-point DIF FFT, so its outputs are in bit reversed order. Therefore, the outputs of N /2-point DIF FFT are bit reversed. The outputs of the two N /2-point FFTs are further processed by the two-parallel butterflies to generate the outputs of N -point FFT in natural order. < final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+