Architecture of a Reusable BIST Engine for Detection and Autocorrection of Memory Failures and for IO Debug, Validation, Link Training, and Power Optimization on 14-nm SoC

Product Description

Architecture of a Reusable BIST Engine for Detection and Autocorrection of Memory Failures and for IO Debug, Validation, Link Training, and Power Optimization on 14-nm SoC

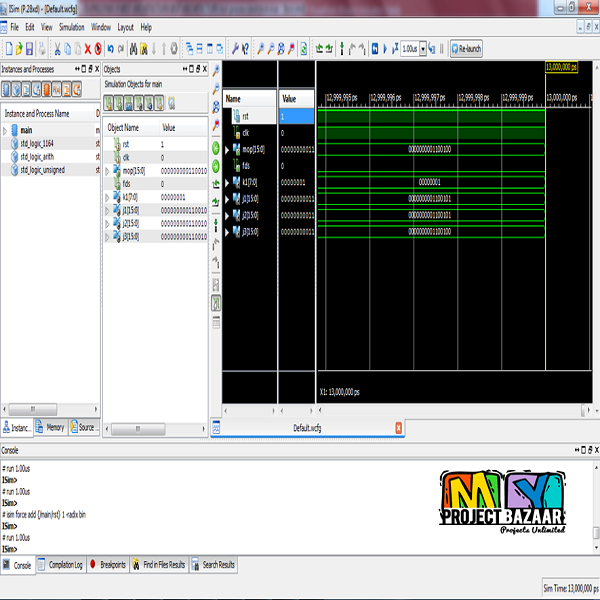

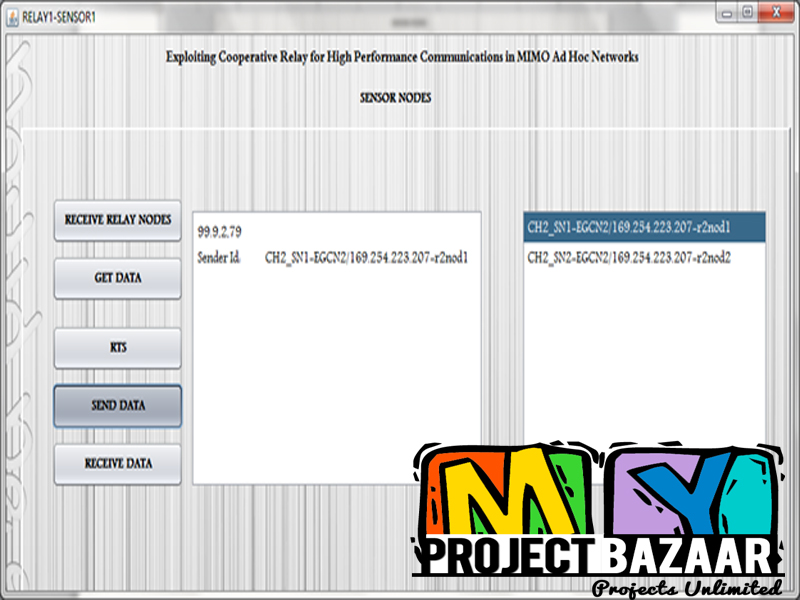

Abstract— The CPGC reusable BIST engine introduced an optional hardware repair engine that works in conjunction with software to provide autorepair technology. This repair capability has been adopted by the JEDEC as a part of the WIO industry standard, known as post package repair (PPR). I n a high – volume manufacturing (HVM) environment, the automatic test equipment (ATE) can use the C P GC row hammer to detect memo r y cell defects. At the end of the detection phase of the test, the ATE test flow could initiate either a hardware automatic or a software assisted manual repair of the failed memory cells using spare row s o f t h e DR A M device. The PPR JEDEC standard has been adopted by DR AM device manufacturers. Specifically, future DR A M are built with extra spare rows of memory to compensate for the increased likelihood of memory cell failures. The automatic modes require no operator intervention, thus significantly reducing H VM test time from many minutes down to seconds. The rest of this article will be structured as follows. In Architecture of second-generation BIST engine for 14-nm SoC memor y and IO, the architecture of CPGC is presented. CPGC software infrastructure architecture details the software architecture.< final year projects >

Including Packages

Our Specialization

Support Service

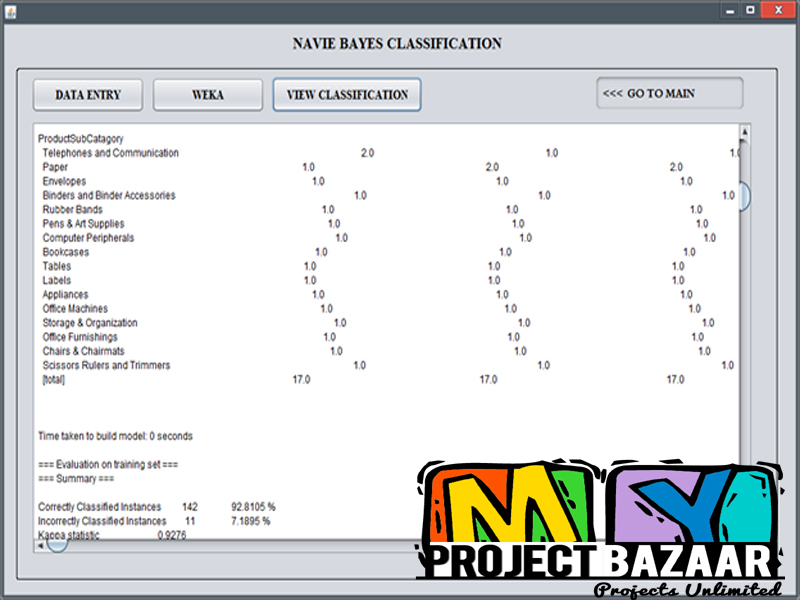

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+