Stable, Reliable and Bit-Interleaving 12T SRAM for Space Applications: A Device Circuit Co-design

Product Description

Stable, Reliable and Bit-Interleaving 12T SRAM for

Space Applications: A Device Circuit Co-design

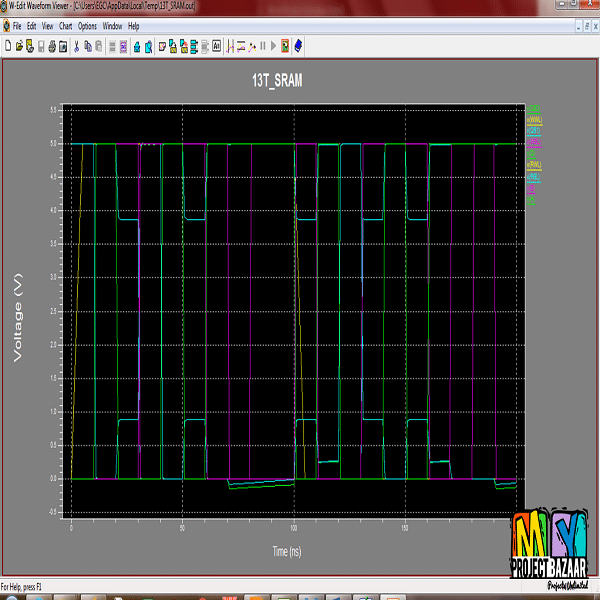

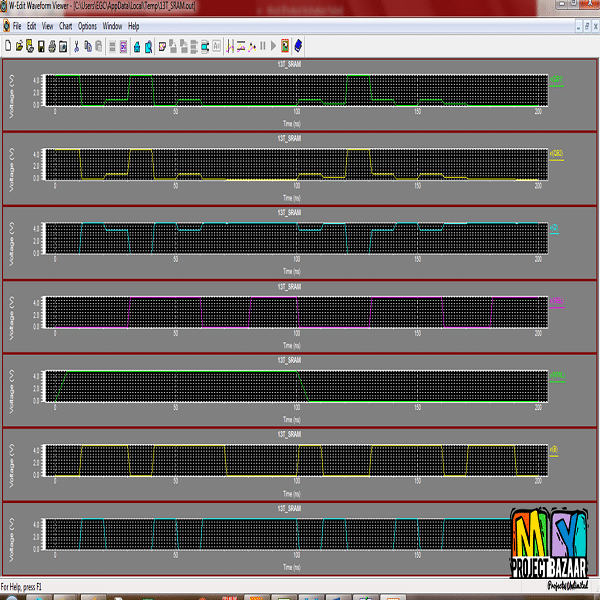

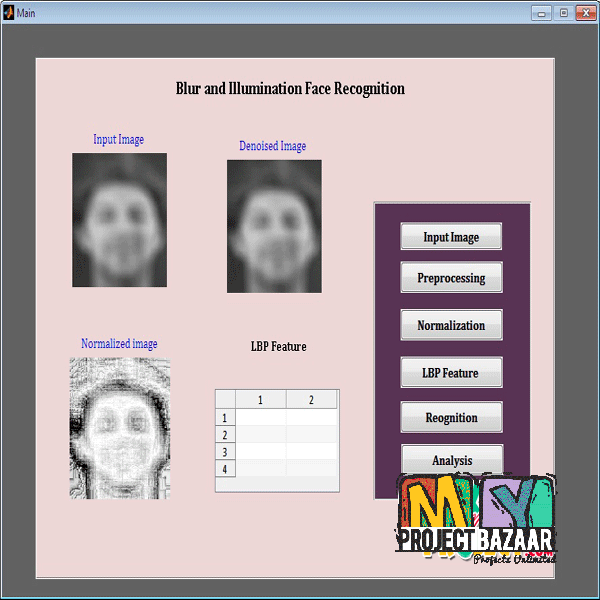

Abstract– Space applications demand highly stable and reliable SRAM circuits for secure and the uninterrupted operation. In this paper, we propose advanced FinFET and self-refreshing logic based 12T SRAM cell (WWL12T). The dual-k gate insulator and symmetric spacer are used to improve the reliability and performance of the FinFET. The outer side high-k insulator reduces the charge trapping to the gate oxide and improves the ON current along with reduced short channel effects. WWL12T Uses extra word line for bit interleaving aware design and a feedback circuit for stable space applications. In the read operation, the extra P-type transistors are active according to stored data bits and charge the storing nodes using bit-line voltages. The static noise margin and word line write margin of proposed WWL12T SRAM cell under worst case process variation (PV) and single charge trapping (SCT) improve by 6.4% and 8.4%, respectively compared to existing 12T SRAM.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+