Reliability Enhancement of Low-Power Sequential Circuits Using Reconfigurable Pulsed Latches

Product Description

Reliability Enhancement of Low-Power Sequential Circuits Using Reconfigurable Pulsed Latches

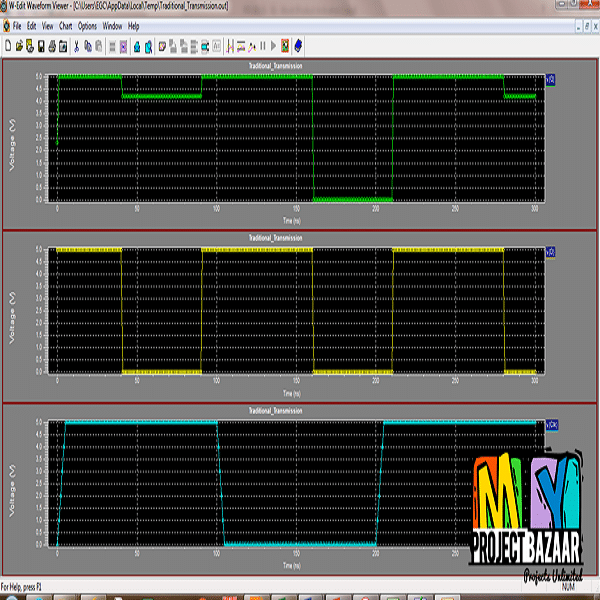

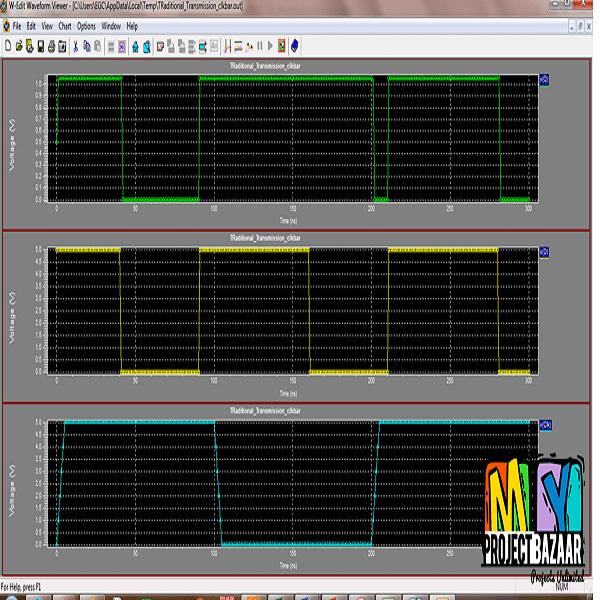

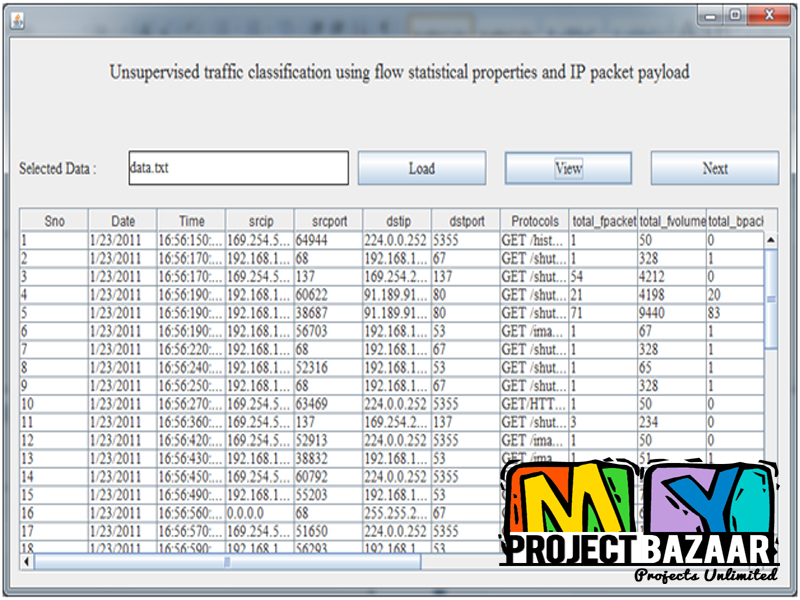

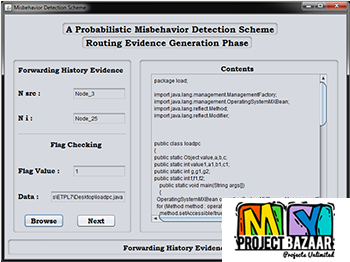

Abstract– Pulsed latches are gaining increased visibility in low-power ASIC designs. They provide an alternative sequential element with high performance and low area and power consumption, taking advantage of both latch and flip-flop features. While the circuit reliability and robustness against different process, voltage, and temperature variations are considered as critical issues with current technologies, no significant reliability

study was proposed for pulsed latch circuits. In this paper, we present a study on the effect of different PVT variations on the behavior of pulsed latches, considering the effect on both the pulser and the latch. In addition, two novel design approaches are presented to enhance the reliability of pulsed latch circuits, while keeping their main advantages of high performance, low power, and small area. Experiments performed using Synopsys 28nm PDK demonstrate the ability of the proposed approaches to keep the same reliability level at different supply voltages

and temperatures in the presence of process variations, with a very small area overhead of around 3%. The two proposed designs have negligible power overhead when running at nominal supply voltage, and they have higher yield per unit power when compared with the traditional design at different voltages and temperatures.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+