A Power-Efficient Reconfigurable Output-Capacitor-Less Low-Drop-Out Regulator for Low-Power Analog Sensing Front-End

Product Description

A Power-Efficient Reconfigurable Output-Capacitor-Less Low-Drop-Out Regulator for Low-Power Analog Sensing Front-End

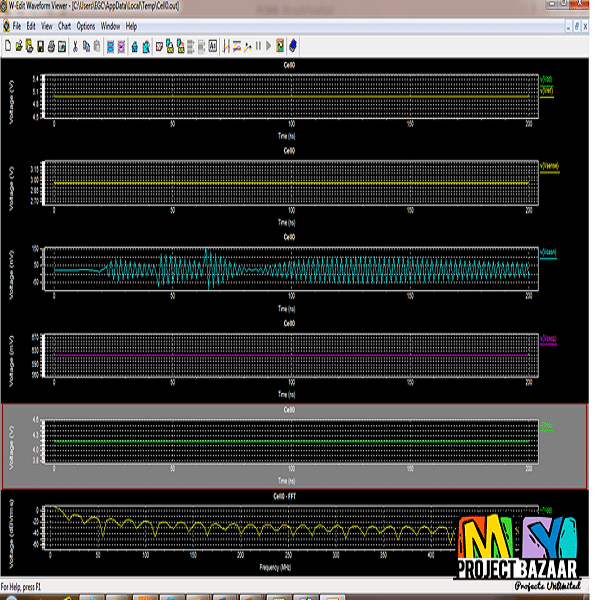

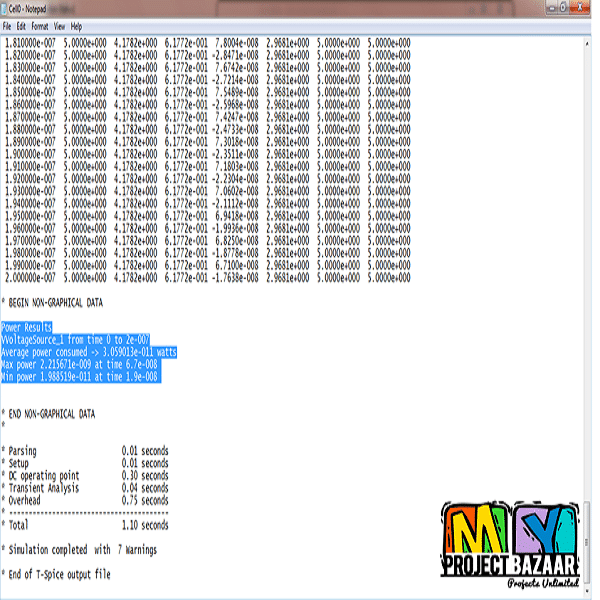

Abstract-A power efficient reconfigurable output-capacitorless (OCL) low-drop-out (LDO) voltage regulator for low-power analog sensing front-end is proposed in this paper. This LDO consists of a floating-gate nMOS pass transistor, an adaptively biased error amplifier, and capacitive circuits for voltage reference generation and for feedback sensing. The error amplifier adopts a class-AB input differential pair and an adaptively biased

regulated cascode topology to improve transient response under the stringent constraint of low quiescent current consumption. The reference voltage is implemented by programming charges on capacitors without employing a bandgap circuit. A prototype chip is designed and fabricated in a 0.35 μm CMOS process to demonstrate the reconfigurability and to validate the performance. The output voltage can be programmed in continuum in the range of 1.2 V to 2.5 V with measured temperature coefficients less than 45 ppm/◦C. The maximum load current is designed to be 1 mA with output voltage drop less than 0.1%. With programmable quiescent current levels less than 1 μA, the current efficiency is higher than 99.9%. From measurements, the line regulation is 0.17 mV/V or −75 dB. The designed OCL LDO remains stable with maximum output load capacitance up to 1 nF under the zero load condition.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+