New Approach to VLSI Buffer Modeling, Considering Overshooting Effect

Product Description

New Approach to VLSI Buffer Modeling, Considering Overshooting Effect

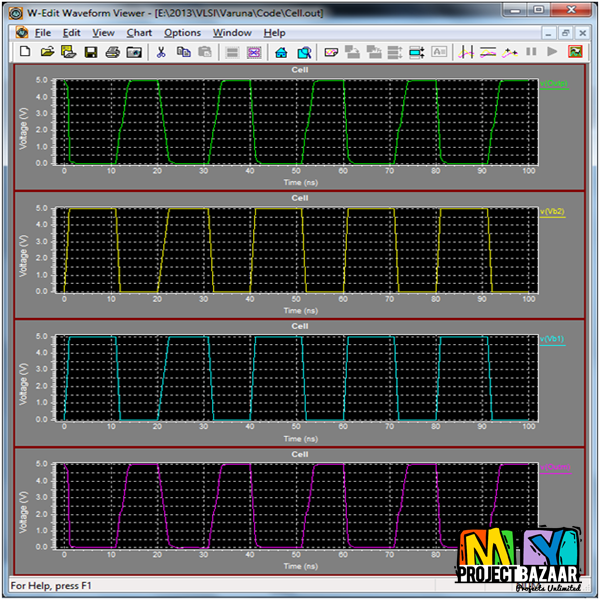

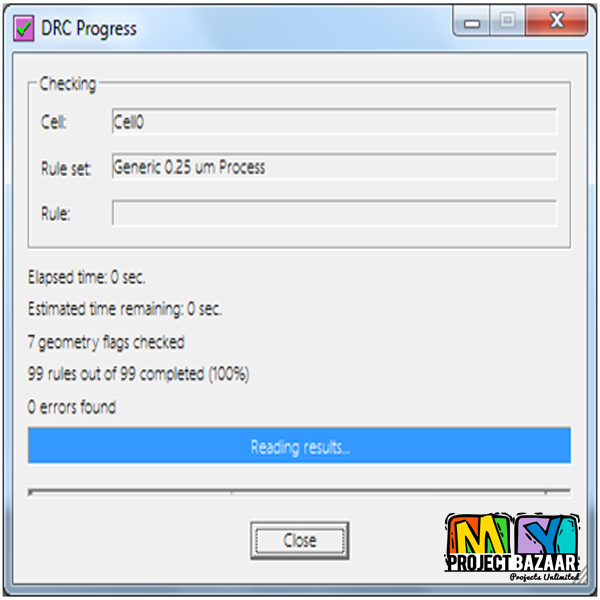

Abstract—New Approach to VLSI Buffer Modeling, Considering Overshooting Effect. we use the alpha power law model for MOS devices to reach a more accurate modeling of CMOS buffers in very deep submicrometer technologies. We derive alpha model parameters of a CMOS buffer for 90-, 65-, and 45-nm technologies using HSPICE simulations. By analytical efforts we find the output resistance of a minimum-size buffer and compare it with those extracted from HSPICE simulations. We propose a new model for the output resistance of a given-size buffer in any technology, which demonstrates 3% error on average as opposed to the conventional model. Also a new buffer resistance is proposed analytically and numerically < Final Year Projects > to calculate the crosstalk for interconnect analysis applications. In addition, we propose a model for the transfer function zero generated by the gate-drain capacitances of MOS transistors, which cause the overshooting effect, and develop an accurate expression for modeling this phenomenon. As the final point, together with the input-to-output capacitance, the equivalent output resistors present a simple and accurate macromodel for the CMOS buffer.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+