Low-Computing-Load, High-Parallelism Detection Method based on Chebyshev Iteration for Massive MIMO Systems with VLSI Architecture

Product Description

Low-Computing-Load, High-Parallelism Detection

Method based on Chebyshev Iteration for Massive

MIMO Systems with VLSI Architecture

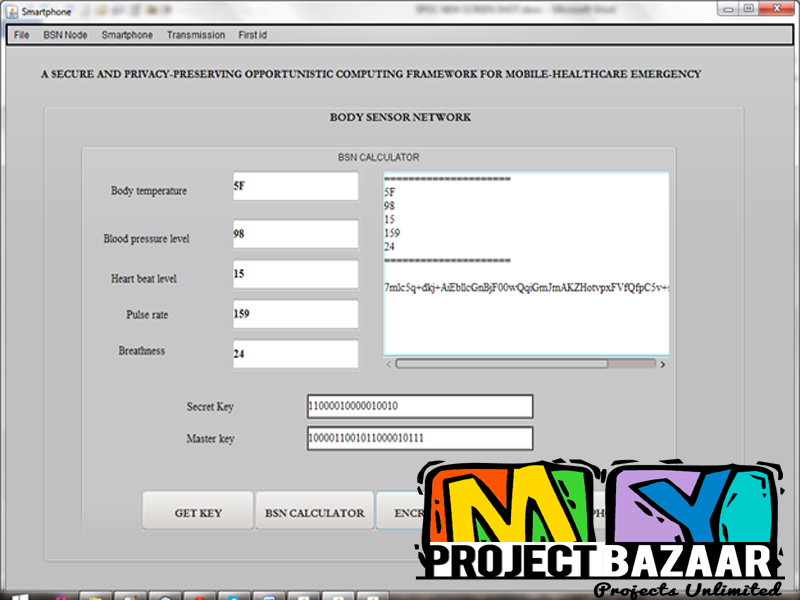

Abstract-Minimum-mean-square-error (MMSE) detection is becoming increasingly relevant in signal detection for massive multiple-input-multiple-output (MIMO) systems because of the increasing numbers of both users and antennas. This paper proposes a signal detection method called parallelizable Chebyshev iteration (PCI) that reduces the computing load and explores the potential parallelism of matrix inversions and multiplications,

which are both major issues in MMSE detection. First, an eigenvalue-approximation-based method is used to obtain an

initial solution. Then, optimized Chebyshev iteration is applied for the approximate computation of matrix inversions and multiplications. The PCI method eliminates the correlations in large-scale matrix inversions and multiplications, thereby improving the parallelism among elements of the estimated vector. These improvements are achieved at the cost of a minor reduction in detection accuracy. Based on the PCI method, a very-large-scale-integration (VLSI) fully pipelined architecture with regular processing elements is proposed to realize 128×16 64-QAM MMSE detection. Here, the iterative parameters are obtained through approximate computations and are used repeatedly, and the user-level pipeline processing pattern achieves an optimal trade-off among the throughput, area and power. This architecture was verified on an FPGA, and the layout was implemented using TSMC 65 nm 1P9M CMOS technology. Results of 2.46 Gbps/W (throughput/power) and 0.53 Gbps/mm2 (throughput/area) were obtained, which represent increases of 4.56× and 3.79×, respectively, compared with current state-of-the-art designs.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+