High- Throughput Area – Efficient Processor for Cryptography

Product Description

High- Throughput Area – Efficient Processor for Cryptography

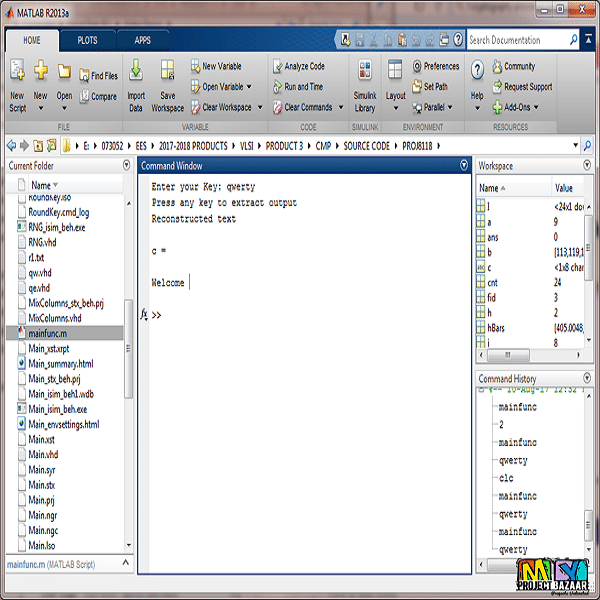

Abstract-Cryptography circuits for portable electronic devices provide user authentication and secure data communication. These circuits should, achieve high performance, occupy small chip area , and handle several cryptographic algorithms. This paper proposes a high performance ASIP ( Application specific instruction set

processor ) for five standard cryptographic algorithms including both block ciphers ( AES, Camellia ,and ARIA) and

stream ciphers ( ZUC and SNOW 3 G) . The processor reaches ASIC -like performance such as 11.6G b/s for AES

encryption, 16.0G b/s for ZUC , and 32.0G b/s for SNOW 3G , etc under the clock frequency of 1.0 GHz with the area

consumption of 0.56 mm2 (65 nm). Compared with stateof-the-art VLSI designs, our design achieves high performance, low silicon cost, low power consumption, and sufficient programmability. For its programmability, our design can offer algorithm modification when an algorithm supported is unfortunately cracked and invalid to use. The product lifetime of our design can thus be extended

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+