A High-Speed Low-Complexity Modified Radix-25 FFT Processor for Gigabit WPAN Applications

Product Description

A High-Speed Low-Complexity Modified Radix-25 FFT Processor for Gigabit WPAN Applications

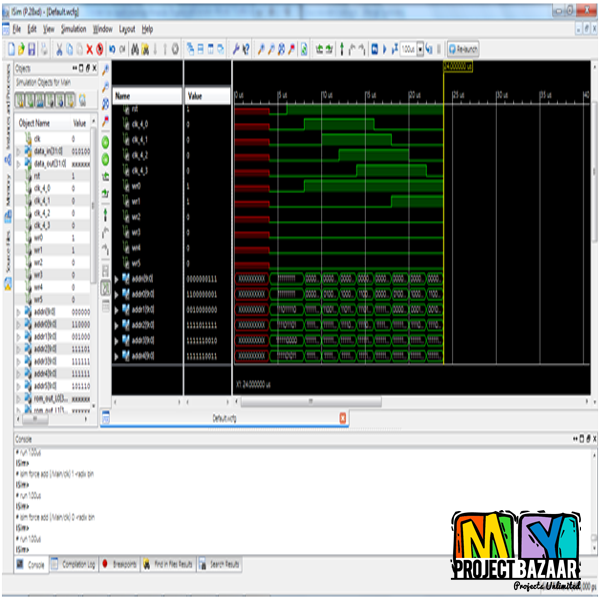

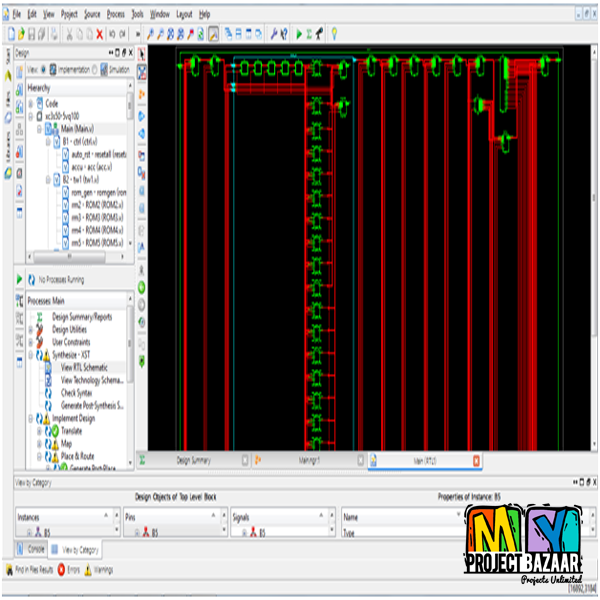

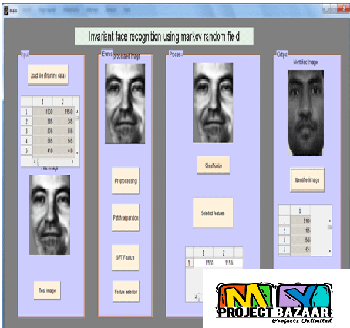

Abstract—a novel modified radix-25 algorithm for 512-point fast Fourier transform (FFT) computation and high-speed eight-parallel data-path architecture for multi-gigabit wireless personal area network (WPAN) systems. The proposed FFT processor can provide a high data throughput and low hardware complexity by using eight-parallel data-path and multi-path delay-feedback (MDF) structure. The modified radix-25 FFT algorithm is also realized in our processor to reduce the number of complex multiplications and twiddle factor look-up tables. The proposed FFT processor has < Final Year Projects > been designed and implemented with 90nm CMOS technology in a supply voltage of 1.2V. The proposed 512-point modified radix-25 FFT/IFFT processor has a throughput rate of up to 2.8 GS/s at 350 MHz while requiring much smaller hardware complexity and low power consumption.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+