169 Products

Recent Posts

- Java Projects For Final Year Students: Top 8 Classic Management Systems That Guarantee Academic & Career Success

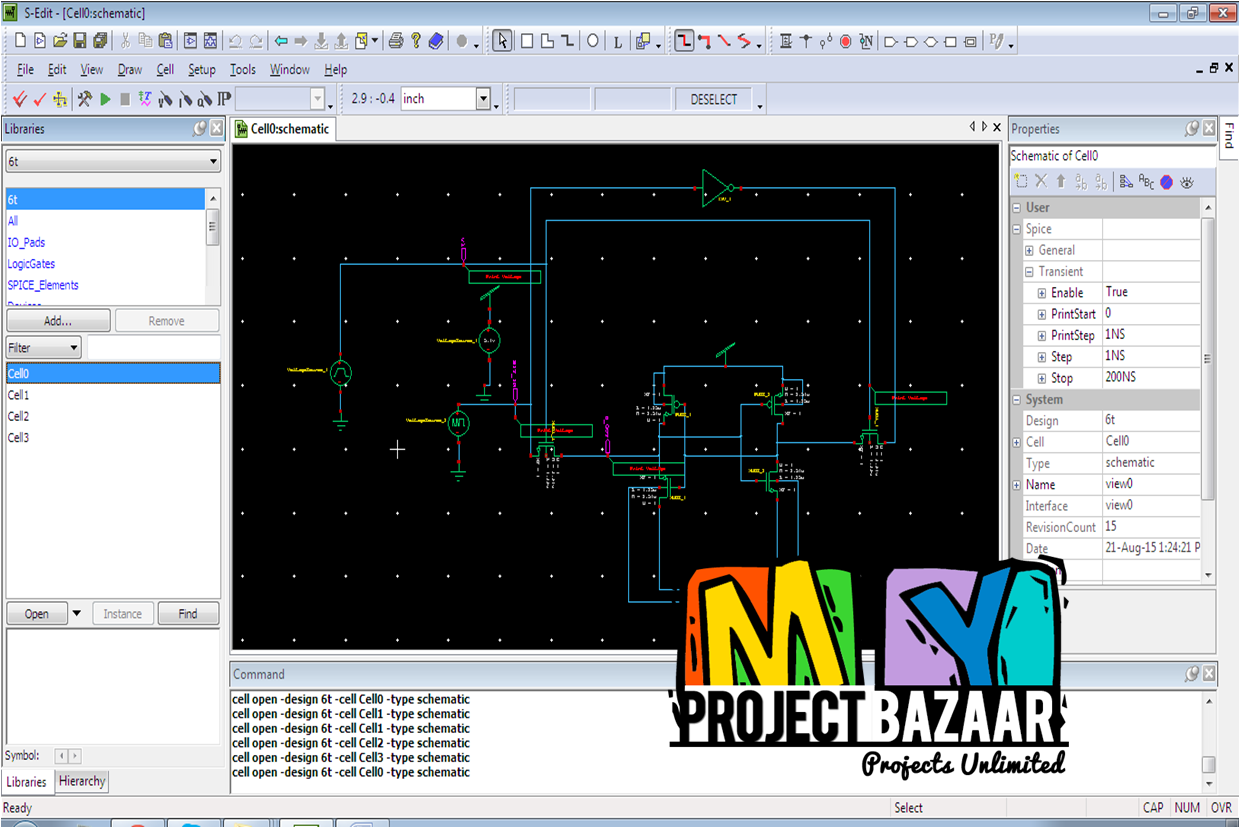

- Top 10 Trending VLSI Cadence Projects for Engineering Students | VLSI Cadence Projects

- Best Final Year Projects for Computer Science Students with Source Code

- Latest technology trends to know before doing final year projects

- Best Final Year Projects 2023

- New Arrivals

- Sale

- Hot items