Design of Power and Area Efficient Approximate Multipliers

Product Description

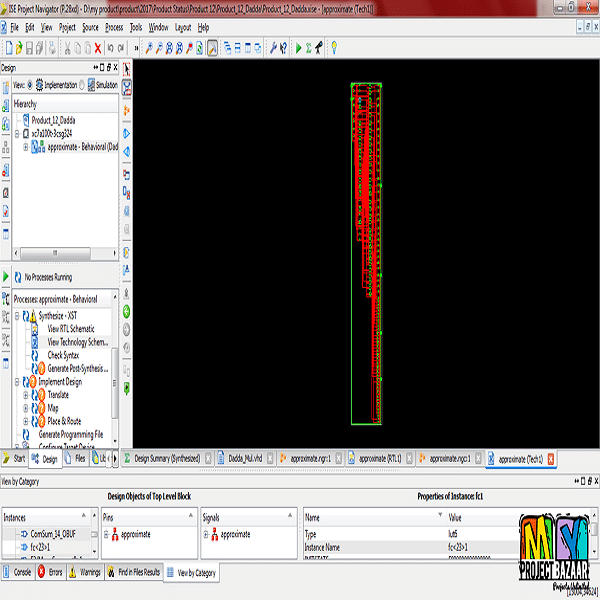

Design of Power and Area Efficient Approximate Multipliers

AbstractIn the first place,computing can decrease the VLSI design complexity with an increase in performance and power efficiency for error resilient applications.In contrast,deals with a new design approach for approximation of multipliers.After all, partial products of the multiplier are altered to introduce varying probability terms. Logic complexity of approximation is varied for the VLSI of altered partial products based on their probability.At the same time,proposed approximation is utilized in two variants of 16-bit multipliers. after all,Synthesis results reveal that two proposed multipliers achieve power savings of 72% and 38%, respectively, compared to an exact multiplier. In fact, better precision when compared to existing approximate multipliers.In short,relative error figures are as low as 7.6% and 0.02% for the proposed approximate multipliers,In the hope that the, previous works. Performance of the proposed multipliers is evaluated with an image processing application,In the final analysis,one of the proposed models achieves the highest peak signal to noise ratio.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+