Design of Low-Voltage High-Speed CMLD-Latches in Nanometer CMOS Technologies

Product Description

Design of Low-Voltage High-Speed CML D-Latches

in Nanometer CMOS Technologies

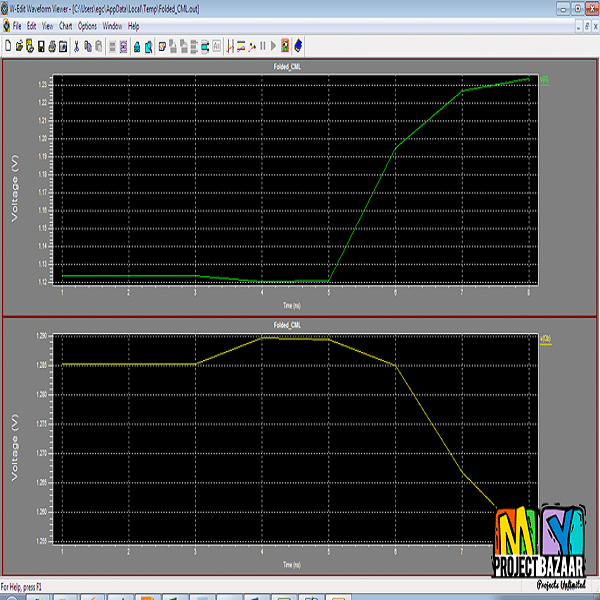

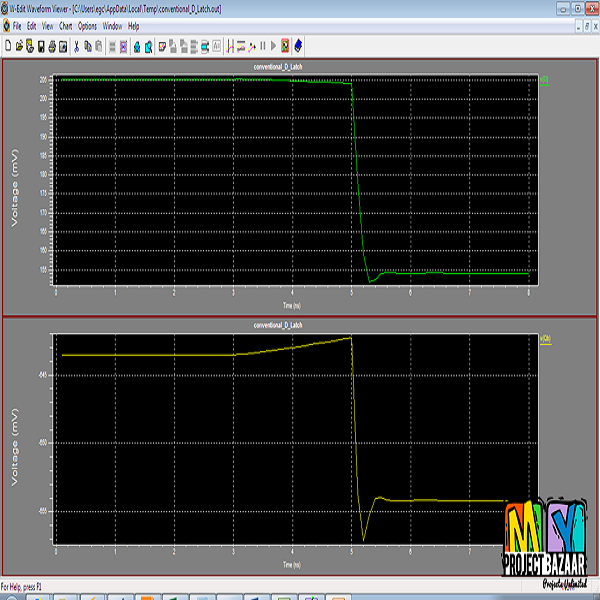

Abstract-In the first placa, presents the design of a novel low-voltage high-speed D-latch circuit suitable for nanometer CMOS technologies. The proposed topology is compared against the low-voltage triple-tail D-latch and its advantages are demonstrated both by simulations, under different performance/power consumption tradeoffs with a 40-nm CMOS technology, and theoretically, thanks to a simple model of the propagation delay derived for both low-voltage topologies. In order to further demonstrate the advantages of the proposed topology, it has also been used to design a D flip-flop (DFF), where thanks to the feature to need just 1 clock differential pair; a further speed improvement is achieved over the conventional triple-tail topology. Indeed, by comparing a two-stage frequency divider designed using both the triple-tail DFF and the proposed folded DFF, a 54% improvement in the maximum operating frequency is found when using the proposed folded DFF.

Including Packages

Our Specialization

Support Service

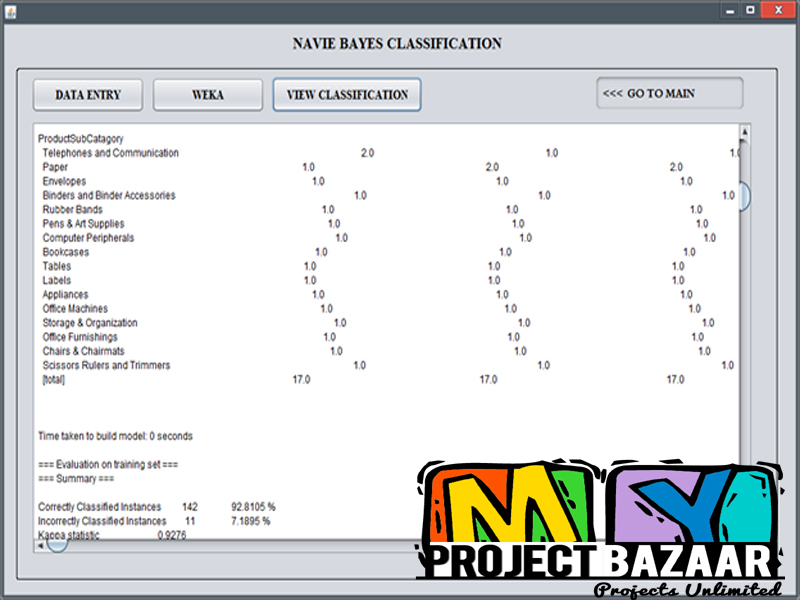

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+