DC-Link Capacitor Current Ripple Reduction in DPWM based Back-to-back Converters

Product Description

DC-Link Capacitor Current Ripple Reduction

in DPWM based Back-to-back Converters

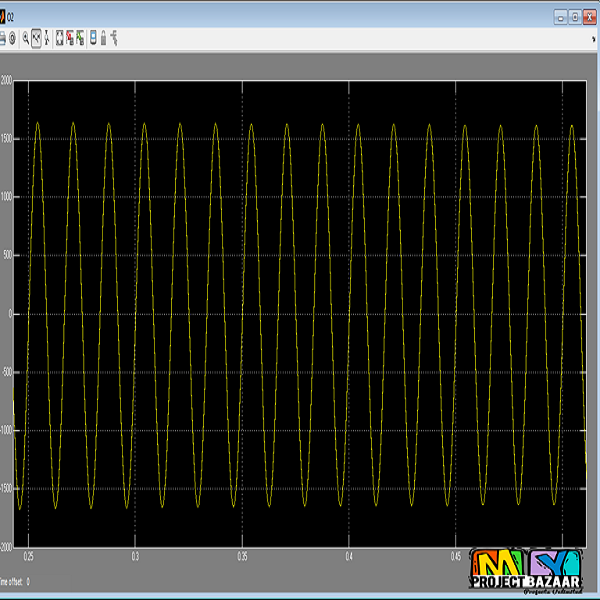

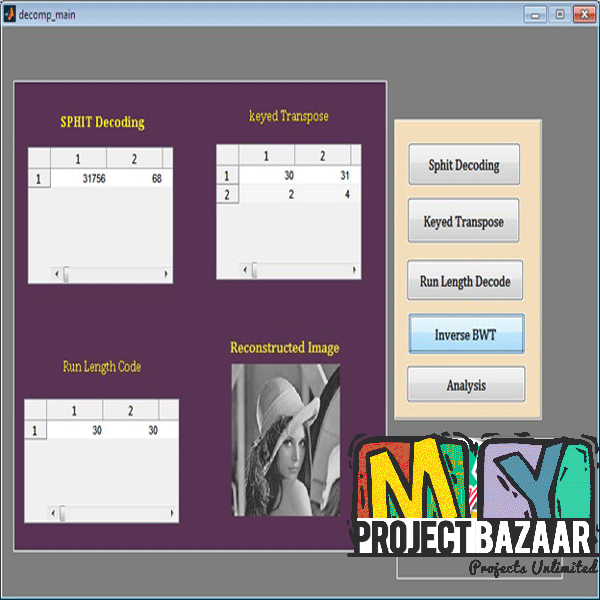

Abstract– In the first place, proposes an improved offset selection method for discontinuous pulse-width modulation (DPWM)- based back-to-back converters to reduce DC-Link current ripple. DPWM is introduced to power converters to diminish the stress on power transistors and prolong their lifespan. However, when using the DPWM method, the DC-Link current ripple is increased in non-switching regions of the power transistors. Moreover, in DPWM-based back-to-back converters, the DC-Link current ripple reaches its maximum when the two transistors of both inverters are clamped in opposite directions. Therefore, the DC-Link capacitors endure more stress, resulting in decreased life-duration. To overcome this issue, the switching method should consider the clamping periods, when the current ripple increases. This can be achieved by modifying the DPWM offset, so that the clamping states of both converters are matched. The effectiveness of the proposed method is confirmed by both simulation and experimental results.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains | |

|---|---|

| Programming Language |