Pre-Charged Local Bit-Line Sharing SRAM Architecture for Near-Threshold Operation

Product Description

Pre-Charged Local Bit-Line Sharing SRAM

Architecture for Near-Threshold Operation

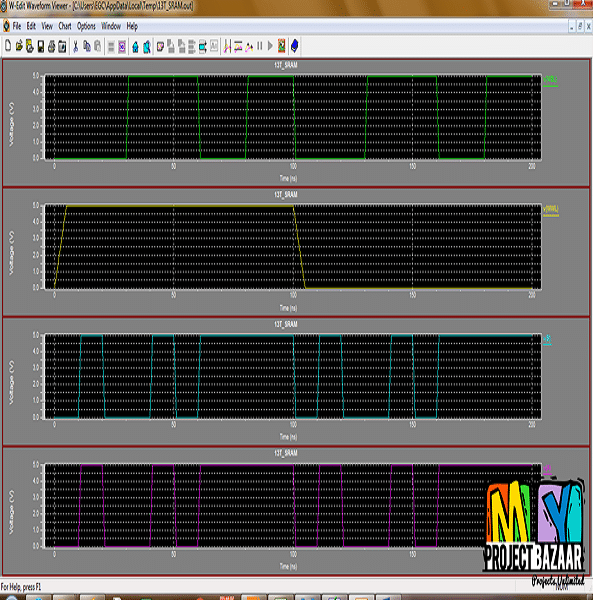

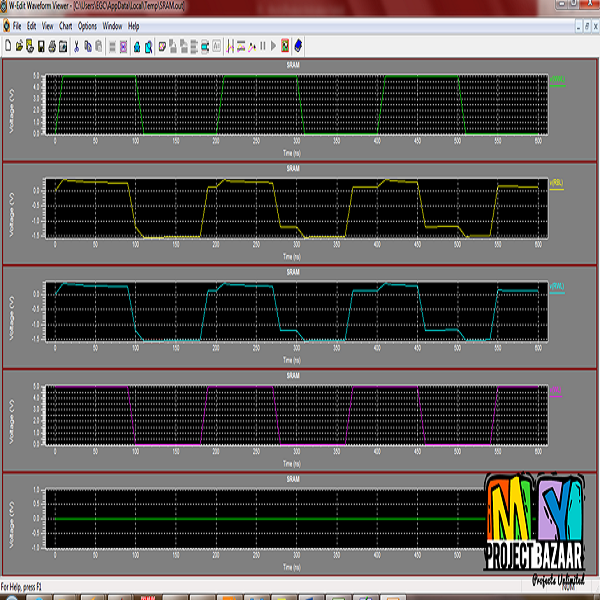

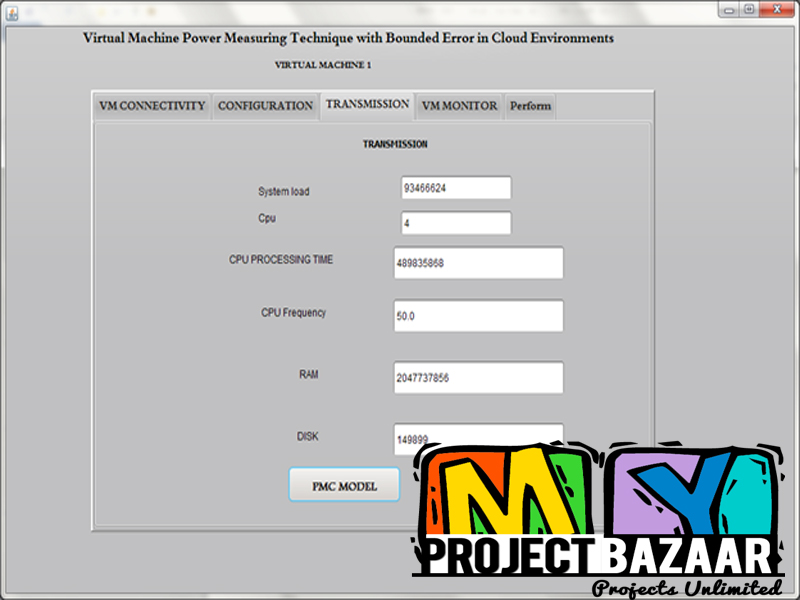

Abstract– In the first place, a pre-charged local bit-line sharing (PCLBS) static random access memory (SRAM) for nearthreshold operation is proposed. In previous local bit-line sharing SRAMs, such as average-8T and full-swing local bit-line (FSLB) SRAMs, multiple bit-cells share a local bit-line pair with a small capacitance for high read stability. However, the average- 8T SRAM has a considerably large delay because the full development of the local bit-line cannot be achieved. On the other hand, the FSLB SRAM reduces the delay but requires a timing constraint of control signals to achieve sufficient read sensing margin. The proposed PCLBS SRAM achieves high read

speed by fully developing local bit-line pair without a timing constraint. Furthermore, the proposed PCLBS SRAM enhances the read stability and the write ability by, respectively, applying a pre-charged local bit-line scheme and transmission gates in write paths. Based on a 22-nm FinFET technology, the FSLB and proposed PCLBS SRAM have the minimum operating voltages of 0.44 and 0.4 V, respectively, while achieving the 5σ target read stability and write ability yields. Compared with the FSLB SRAM, the proposed PCLBS SRAM consumes 21% less energy at each minimum perating voltage and has 57% smaller read delay at the operating voltage of 0.4 V

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+